Space Vector Pulse-Width Modulation for Multilevel Multiphase Voltage-Source Converters

Abstract

The space vector pulse-width modulation (SVPWM) for multilevel multiphase power converters is studied in this dissertation. Multilevel converters have a high voltage capability with voltage limited devices, high efficiency, low harmonic distortion and good electromagnetic compatibility. Multiphase machines have a high reliability, high efficiency and low torque ripple with a low per-phase power ratting. The multilevel multiphase technology combines the benefits of both technologies, but new modulation techniques must be developed to take advantage of multilevel multiphase converters.

The SVPWM technique has been deeply studied for multilevel converters due to its performance benefits when compared with other modulation techniques. However, even though it has a general acceptance in three-phase applications it has hardly been studied in relation to multiphase systems. Most of multiphase SVPWM algorithms presented in literature deal with two-level converters. Multilevel multiphase SVPWM algorithms are rare and most of them have been developed for a particular number of phases or levels, and it is difficult to extend them to other cases. There are some generic algorithms available but they are complex and not suitable for real-time implementation. The main objective of this work is to develop a generic SVPWM algorithm for multiphase converters, valid for any number of levels and phases that can be implemented in real-time. The main contributions are summarized in the following.

Research starts with the study of the relationships between the switching states of the transistors and the output voltage in the typical multilevel topologies: diode clamped, flying capacitor and cascaded full-bridge converters. Some common characteristics have been identified in those relationships, which allow formulating the SVPWM problem in a generic form for all these topologies. Novel expressions to calculate the number of redundant switching states corresponding to the same output level are also provided.

Next, two well-known multilevel three-phase SVPWM techniques, one with and another without switching state redundancy, are studied to identify the key issues in the implementation of SVPWM algorithms. The most significant are two: the high number of power switches that must be controlled in parallel in multilevel topologies; and the extra modulation complexity due to the switching state redundancy present in converters with no neutral wire. Redundancy can be used to achieve certain control goals such as modulation index extension, capacitor voltage balancing, dc source current control, switching frequency reduction, fault tolerance or common-mode voltage elimination. Field-programmable gate arrays (FPGAs), with their concurrent processing capability, are identified as appropriate devices for implementing multilevel modulation algorithms. A new modular design of the hardware implementation and a comparative analysis of both modulation algorithms are carried out.

Finally, two novel SVPWM algorithms for multilevel multiphase voltage source converters, with and without switching state redundancy, are developed. Both are formulated in a multidimensional space and can be applied to converters with any number of levels and phases. It is demonstrated, in both cases, that the multilevel SVPWM can be carried out by means of a two-level space vector modulator without redundancy. Therefore, a new two-level multiphase SVPWM algorithm is developed. In the case of multilevel P-phase converters without redundancy, the SVPWM algorithm is based on a displacement plus the new two-level SVPWM for P-phases. In the case of a multilevel P-phase converter with switching state redundancy the SVPWM is based on a more complex transformation and the new two-level SVPWM algorithm for (P-1)-phases. This algorithm includes a new technique that makes it easy to choose the switching states among the set of redundant switching states. Both modulation algorithms can be applied to the typical multilevel topologies; they have a low computational complexity and they are suitable for hardware implementation. The new SVPWM algorithms are implemented in a low-cost FPGA and they are tested in laboratory with a five-level five-phase inverter. The modulation techniques are also applied to multilevel three-phase converters with three and four legs. The resulting algorithms are compared with existing SVPWM techniques and tested in laboratory.

Major contributions of this dissertation have been published in five journal papers, and minor contributions have been presented at three international conferences.

Download

Photos

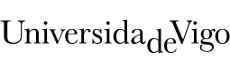

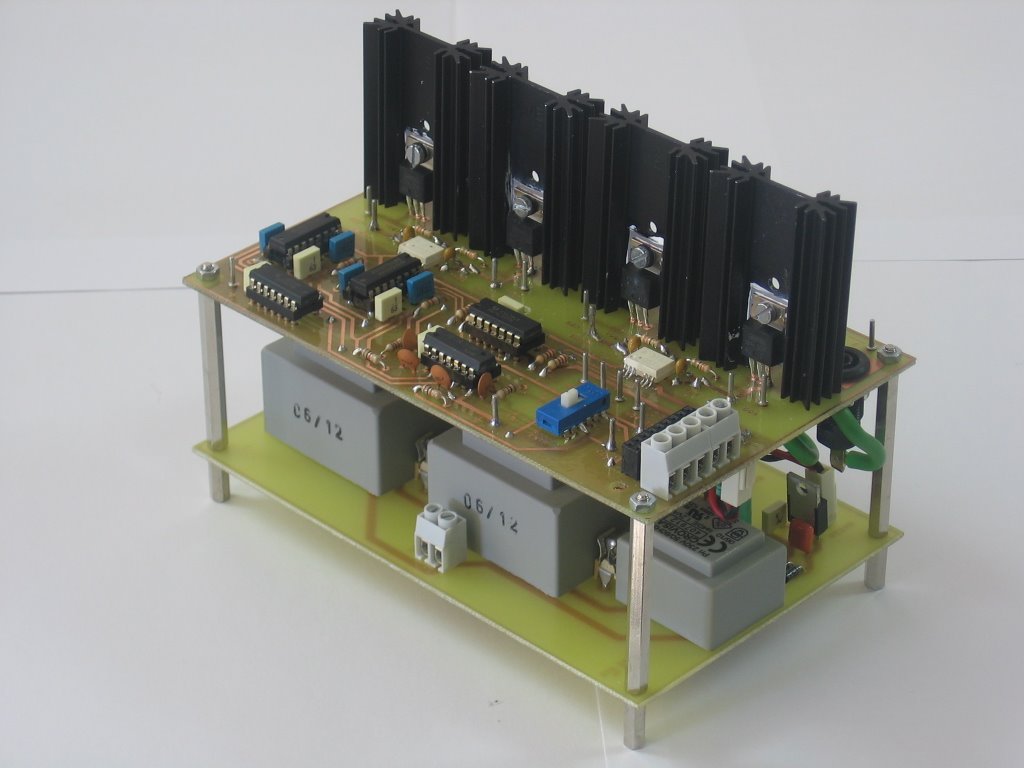

Three-phase neutral point clamped motor drive

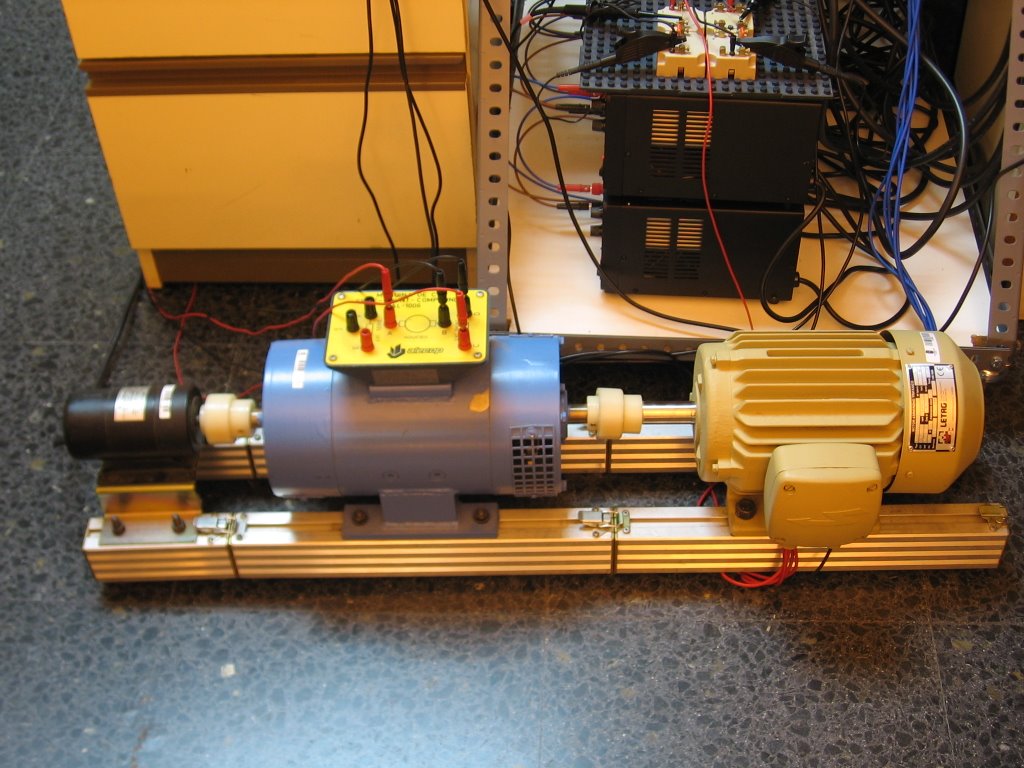

Five-level five-phase motor drive

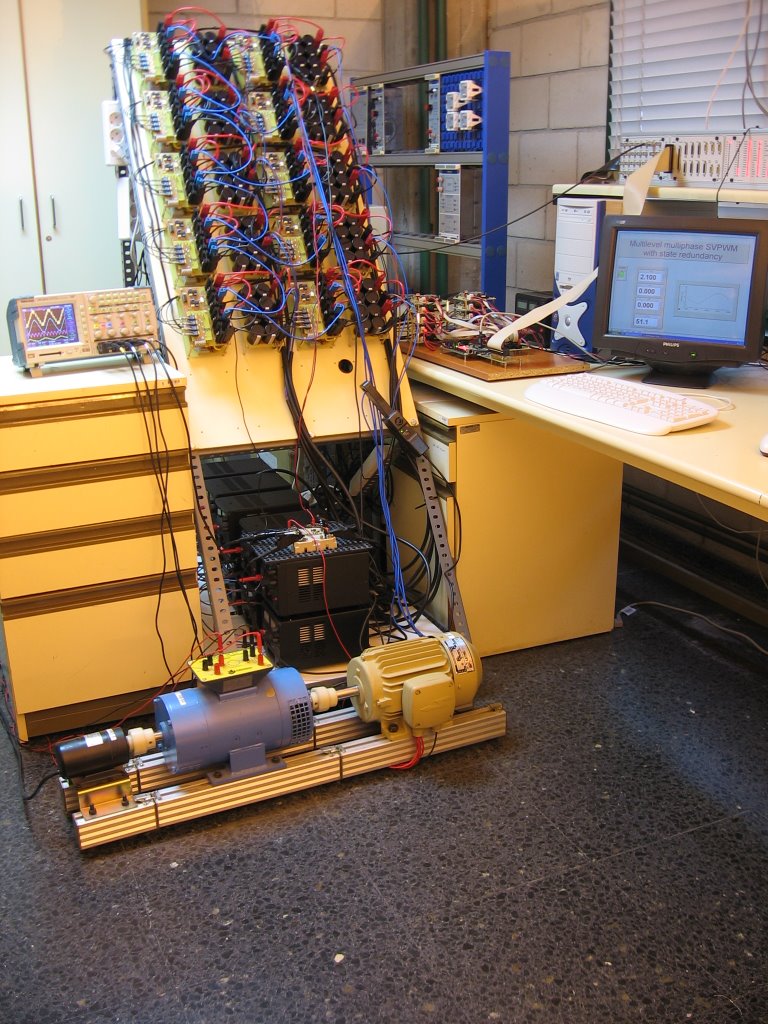

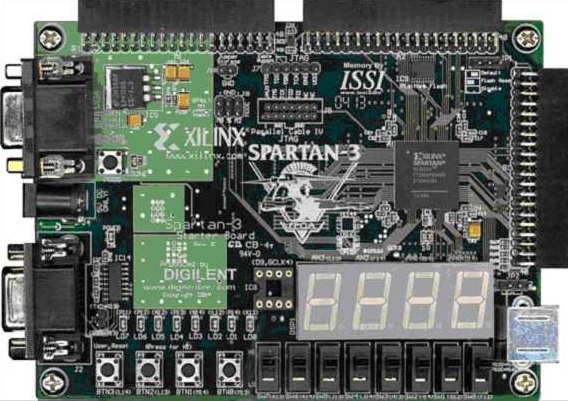

FPGA board

Optical link

Full-bridge inverter

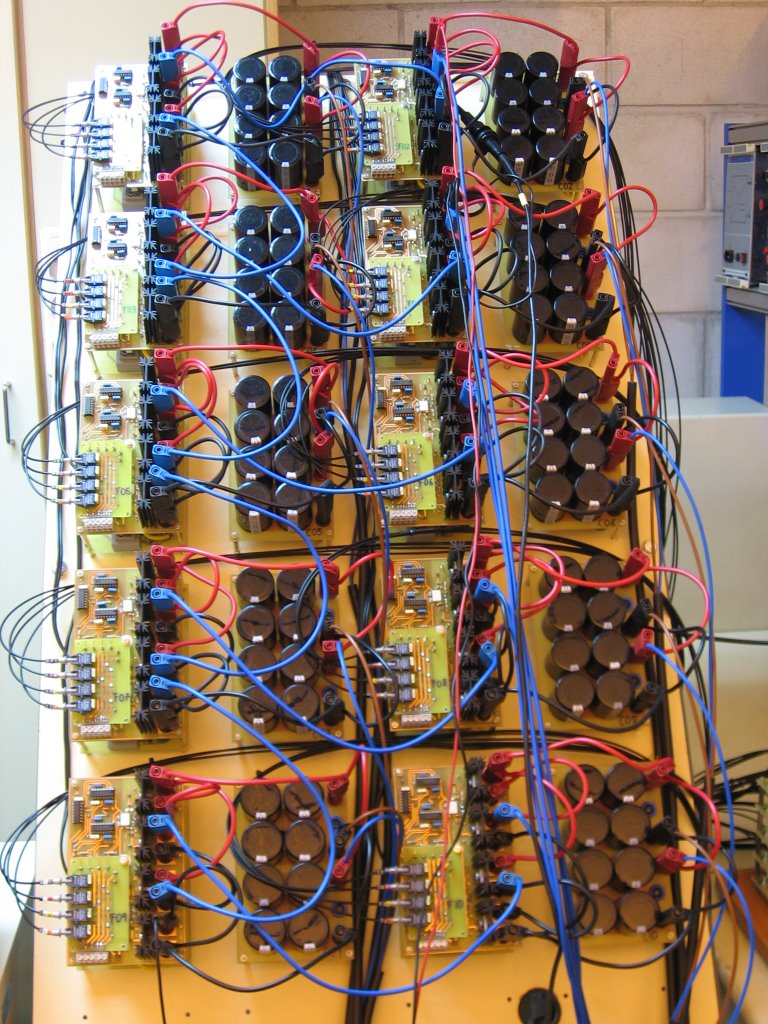

Five-level five-phase cascaded full-bridge inverter

Load

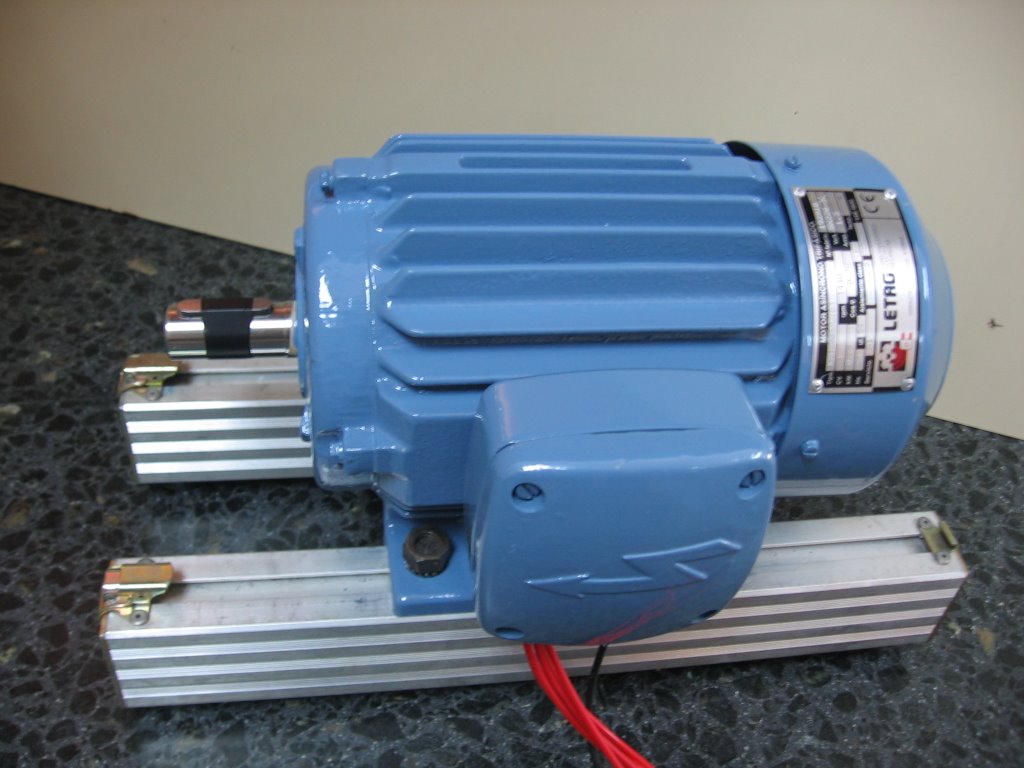

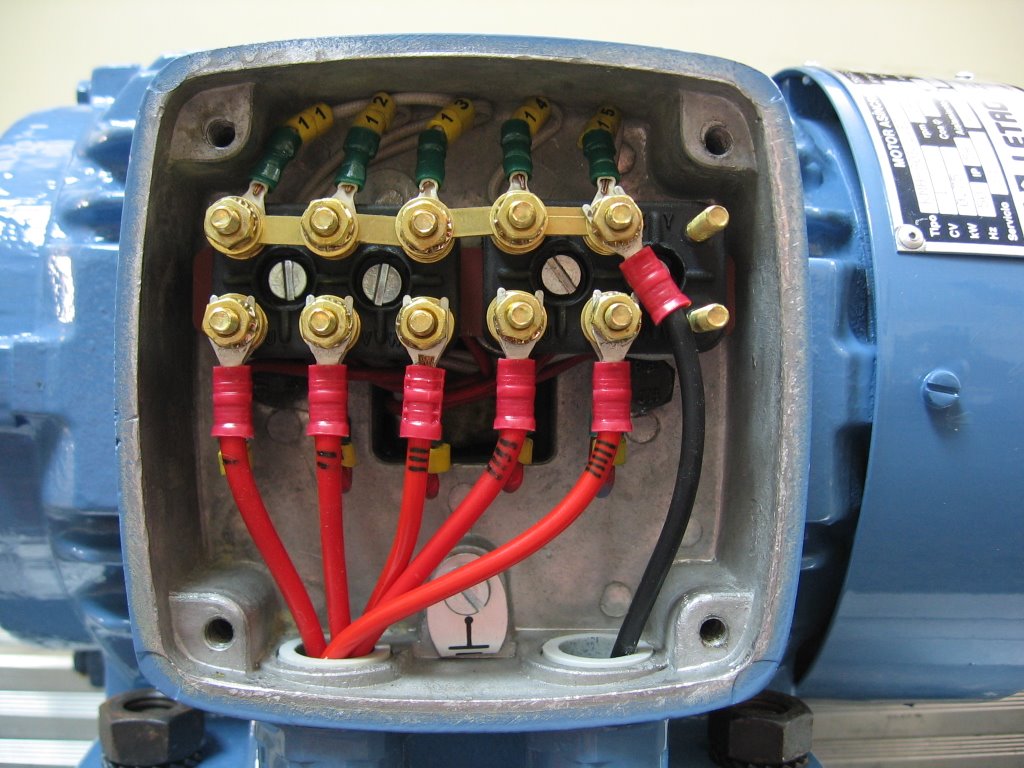

Five-phase induction motor

Star connected five-phase motor